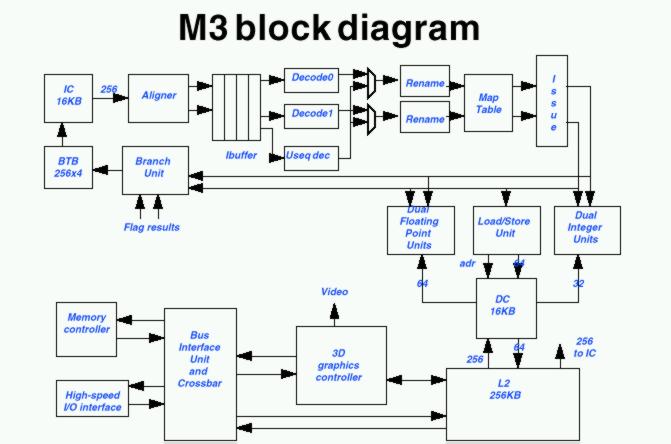

diagrama de bloques.

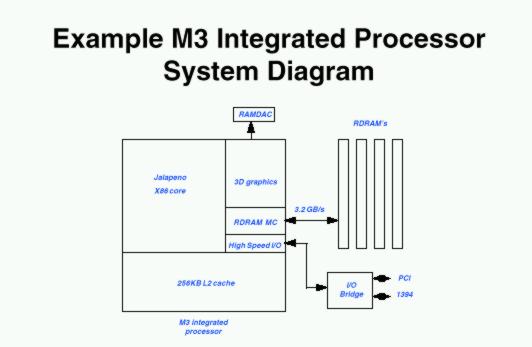

En cuanto a las cualidades tecnicas, Jalapeno incluye un pipeline de 11 estados, además incluye 256 Kb de L2 y 16 Kb de L1 memoria cache en el chip. El chip también integra un controlador gráfico 3-D, lo cual le permite procesar 3 millones de polígonos por segundos. Los objetivos del diseño del procesador Jalapeno (familia de los procesadores M3) son basicamente mejoras a la arquitectura predecesora más que introducir una nueva arquitectura. En este enfoque ellos se concentraron en reducir la latencia de memoria, mejorar el manejo de punto flotante y reducir el tamaño del procesador, además de tener un mejor desempeño en gráficos 3D.

Jalapeno es una arquitectura x86 con ejecución fuera de orden (out-of-order), con dos unidades para calculos con enteros, dos para punto flotante, una para saltos y otra para cargar y almacenar.

Procesador cuenta con pipeline de 11 estados y una frecuencia de reloj de 600 MHz. Ocupa un area de 12 mm^2, en un proceso de .18 micrones. Para la decodificación de instrucciones utilizan predicción de direcciones via la BTB, todas las instrucciones son decodificadas en "nodos". Los nodos contienen la fuente, el destino y la instrucción de control, la mayoria de ellos pueden ser manejados en forma dual y algunos en forma paralela. Estos nodos son formados en los puntos de chequeo, los cuales son 16 activos, lo cual significa que se pueden manipular 96 nodos a la vez.

Con respecto a la cache, contiene 256Kb de L2 y 16Kb de L1. Se utiliza la estrategia de "prefetches" para mejorar desempeño de la memoria, además se puede predecir hasta la mitad de las perdidas desde la L2, esto hace que la los 256Kb se comporten como 512Kb. Por otra parte la velocidad de acceso del procesador a la DRAM es minimizado a través de un controlador de memoria en el chip, el cual asegura <20 ns en el peor de los casos para acceso a una palabra. Este contralador mantiene 32 páginas abiertas, lo cual es más que el promedio del mercado.

La integración del procesador a la memoria que es a través del controlador de memoria, tiene un ancho de banda de 3.2 Gb entre el procesador y el modulo de memoria en linea (RIMM).

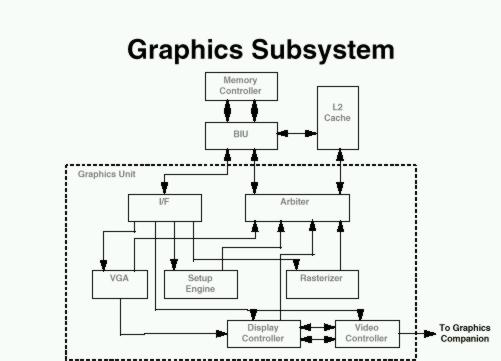

Con respecto al desempeño con gráficos, Jalapeno incorpora en la cache L2 una minicache para texturas, en cuanto al sistema elimina el frame buffer dedicado por su alto costo y permite prefetching de texturas con mínima latencia. Esto le permite un desempeño de 3 mil poligonos por segundo, 266 mil pixels por segundo y 230 MHz "dot clock". Además permite otras cualidades graficas como fog, anti-aliasing, filtros de textura.

Referencias:

Microprocessor Forum: Cyrix serves Jalapeno core

Cyrix